Qingming Festival holiday notice

Qingming Festival holiday notice

Apr .02.2024

On April 4th, it is the traditional Chinese festival Qingming Festival. According to traditional customs, we will return to our hometown to worship, ancestor worship, and tomb sweeping. We will enjoy a three-day holiday and return to our hometown to worsh

Easter Notice

Easter Notice

Mar .29.2024

During the Easter holiday, SIC Electronics’ companies in the United States, Hong Kong, and the United Kingdom are on holiday, but employees of the Chinese company work normally.

Qingming Festival holiday notice

Qingming Festival holiday notice

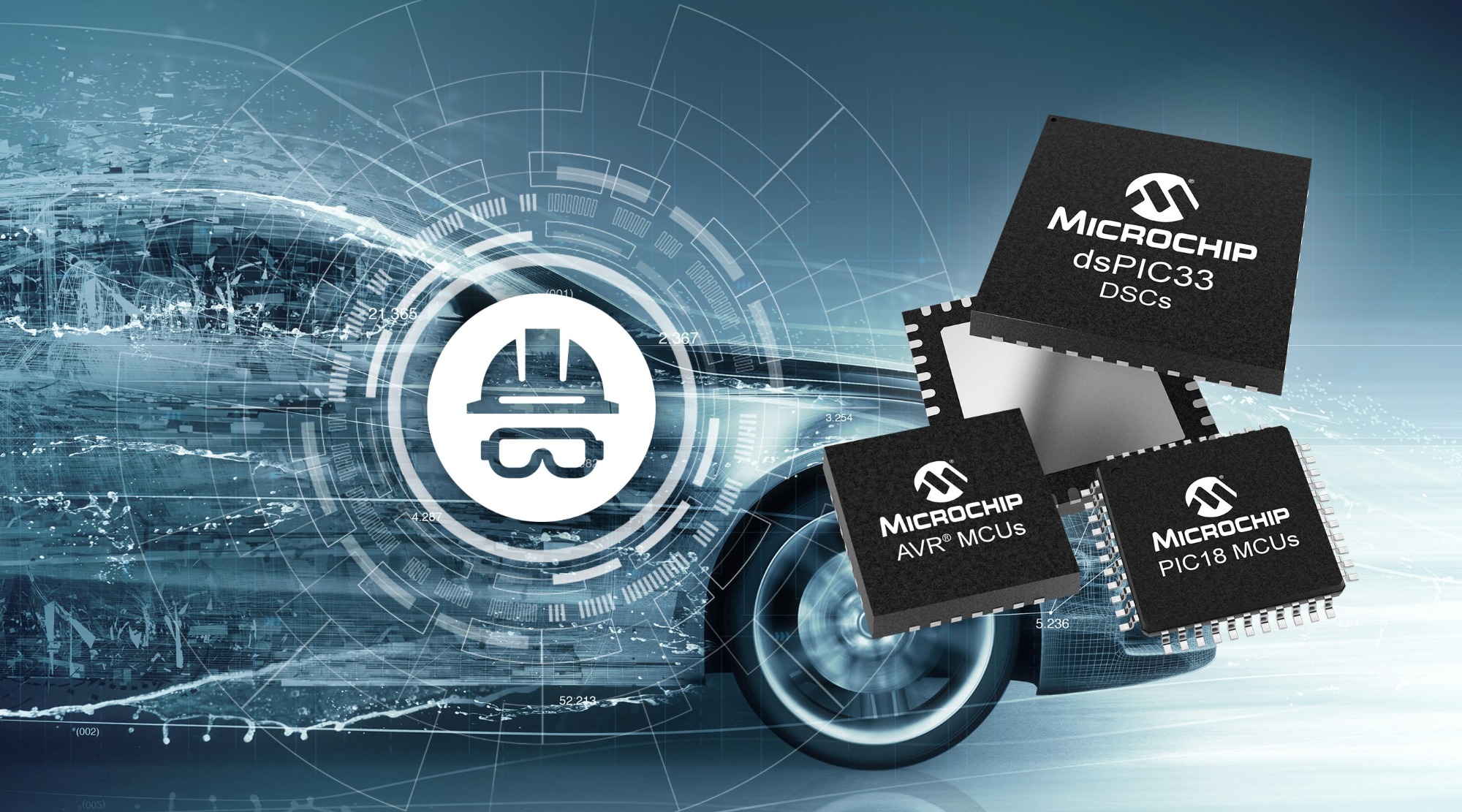

Microchip Technology Announces Qi® v2.0 Compliant, dsPIC33-Based Reference Designs

Microchip Technology Announces Qi® v2.0 Compliant, dsPIC33-Based Reference Designs

Easter Notice

Easter Notice

Infineon launches low-cost, low-power, long-distance Bluetooth module CYW20822-P4TAI040

Infineon launches low-cost, low-power, long-distance Bluetooth module CYW20822-P4TAI040